研究室紹介OPAL-RING

本多 研究室

高性能コンピューティングのためのコンピュータシステム、

計算方式、性能を最大限引き出すユーザ支援技術の開発

| 所属 | 大学院情報システム学研究科 情報システム基盤学専攻 |

|---|---|

| メンバー | 本多 弘樹 教授 |

| 所属学会 | IEEE、ACM、情報処理学会、電子情報通信学会 |

| 研究室HP | http://www.hpc.is.uec.ac.jp/honda/ |

| 印刷用PDF |

掲載情報は2015年8月現在

- 本多 弘樹

Hiroki HONDA

- キーワード

-

高性能コンピューティング、GPUコンピューティング、グリッドコンピューティング、並列化コンパイラ、エンドユーザ支援技術、グリーンコンピューティング、メニーコア・プロセッサ

研究概要

高性能コンピューティングのための並列処理技術の開発

多くのプロセッサを接続したマルチプロセッサシステム上で並列処理を行うことにより、処理の高速化を図る方式が普及している。

また、コンピュータネットワークの高速化にともない、ネットワーク上のコンピュータ群を1つのマルチプロセッサシステムとしてとらえて、並列処理する方式が注目されている。

並列処理による高性能コンピューティングをユーザにとって使いやすいものとするためには、ユーザに並列処理を意識させることなく、コンピュータシステムが自動的に並列処理を行う技術が必要となる。

そこで、当研究室では「高性能コンピューティングのための並列処理技術」と、高性能コンピューティングシステムの性能を引き出す「エンドユーザ支援技術」の開発に取り組んでいる。

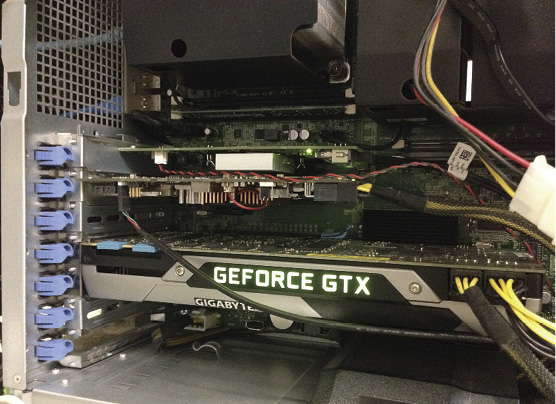

また、コンピュータの単体性能の向上は消費電力の問題から頭打ちになりつつある。そこで、消費電力当たりの性能に優れるGPUやマルチコアプロセッサを「高性能コンピューティング」に適用する研究が注目されている。

ここでは、1チップ上に多数集積されるプロセッサコアをいかに構成し、どのようにその性能を引き出すかということが重要になるため、GPUのプログラミング・利用技術やメニーコア・プロセッサのアーキテクチャ、評価環境等についてソフトウェア・ハードウェア両面から研究開発を行っている。

エンドユーザ支援技術の開発

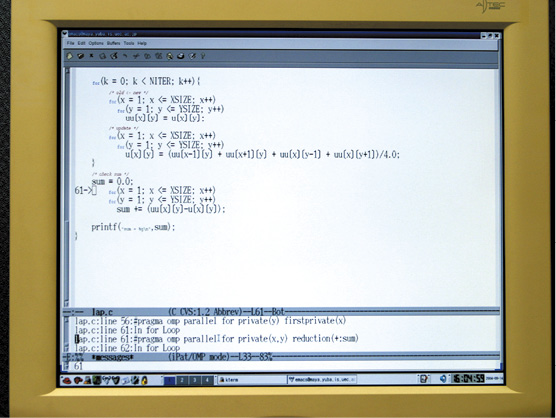

高性能コンピューティングシステムにおいて、潜在的な最高性能を引き出すためには、個別のプログラミング方式を適応して詳細なチューニングを行う必要があり、ユーザに高いプログラミング技能と煩雑なチューニングを強いる。これらを解決するために、ユーザの利用を支援する技術が求められている。

グリッド構築技術の開発

また、グリッド構築のためのミドルウェア技術の開発を進めている。グリッドを構築するためには技術要素として、広域に分散する資源共有技術、協調的な問題解決技術、仮想的な複合組織体の構成・管理技術が必要となる。

本研究室で開発したライブラリの自動遠隔インストール機構やサーバの動的切り替え技術は、グリッド利用の際のユーザの手間を大幅に軽減するものとして注目されている。

グリーンコンピューティング

- 並列化処理ツールiPat/OMP

さらに近年では、地球環境への配慮や電力供給事情の変化、スマートフォンに代表されるモバイル端末の普及など様々な要因によって、コンピュータシステムに対しては、演算性能の向上のみならず、これをいかに少ない消費電力で実現するかという要求が高まっている。このような要求に応えるためには、GPGPUに代表されるアクセラレータの積極的利用による高効率化、半導体の動作周波数と供給電圧を適切にコントロールするDVFS(Dynamic Voltage-Frequency Scaling)や使用しない回路への電力供給を止めるPG(Power Gating)などの技術を適用することが必要となる。

これらの技術を効果的に適用するためにはハードウェアとソフトウェアが協調して動作することが肝要であることから、当研究室では、省電力プロセッサアーキテクチャ、アプリケーションの特性に応じて性能向上と消費電力削減を両立するソフトウェア解析手法、アクセラレータを含む様々な計算資源を適切に利用し性能を引き出す並列処理手法など、幅広い観点から研究を進めている。

アドバンテージ

高性能コンピューティング技術に関わる広範な研究分野を網羅

- GPGPU実験環境

当研究室では、高性能コンピューティングを中心課題として、プロセッサアーキテクチャからシステムアーキテクチャ、システムソフトウェア、アプリケーションに至るまで幅広い分野を対象としている。このため、システム内の要素技術にとらわれることなくシステム全体に視野を広げた研究開発が可能である。

今後の展開

各種並列処理方式を有機的に統合した高性能コンピューティングシステムの構築

- メニーコアチップ・GPGPU混在実験環境

高性能コンピューティング基盤の構築は、消費電力を考慮しつつアプリケーションに内在する並列性を引き出し、チップ内レベルからグリッドのような広域分散環境レベルでの並列処理までを適切に利用することによって達成される。今後は、これまでアプリケーションレベルでそれぞれ開発されてきた並列処理方式を有機的に統合した高性能コンピューティングシステムの構築に取り組みたい。